Complete Verilog HDL programming with Examples and Projects

Fundamentals, Design flow, modeling levels, Datatypes, test bench, Tasks & system tasks, FSM, FPGA & examples & Projects

4.21 (315 reviews)

1,278

students

8 hours

content

Jun 2023

last update

$49.99

regular price

What you will learn

Learning Verilog HDL Programming fundamental concepts and properties compare to C Language, feature & advantages of Verilog HDL over VHDL

VLSI Design flow ( FPGA & ASIC) and Difference between FPGA vs ASIC

Different design methodologies in Verilog HDL programming with examples

Behavioral modeling with blocking & Non-Blocking concepts and real time examples

Test bench Verilog program with examples

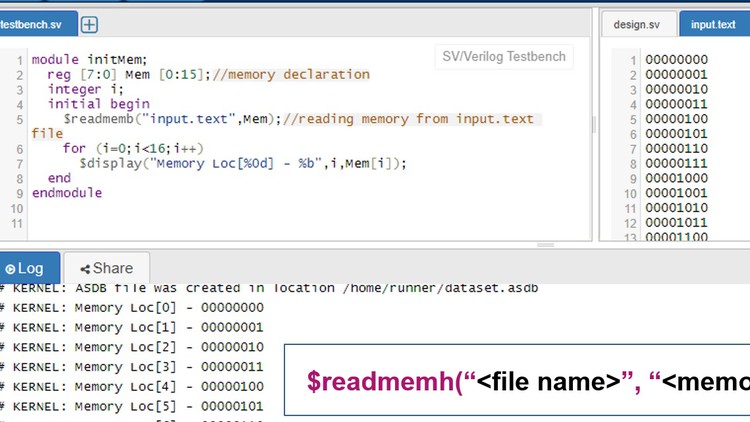

Task & system tasks with examples for random data generator, file based operations and memory load operations, and file representation input & output etc.

Finite state machine (FSM) with example for both Mealy & Moore and Sequence detector FSM

Complete design & test bench programming for Memory controllers

Complete design & test bench programming for FIFO controller

Complete design & test bench programming for Encoder & decoder for Hamming code Error detection correction

Basics of FPGA

Related Topics

3454330

udemy ID

8/27/2020

course created date

9/24/2020

course indexed date

Bot

course submited by