VSD - SoC Design of the PicoRV32 RISCV micro-processor

Freedom to build micro-processors

3.88 (64 reviews)

674

students

4 hours

content

Jun 2018

last update

$39.99

regular price

What you will learn

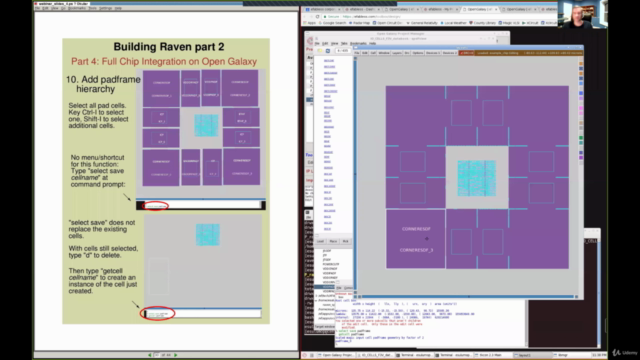

Run a full physical design flow from RTL design to GDSII, making it ready for tape-out.

For freshers, this course will make them industry ready and might increase their chances of getting placed or work for tier-1 company

For experienced VLSI Physical design professionals, this will give a bigger picture of SoC physical design, which is appplication specific

For senior non-VLSI engineers, this course will help them understand the whole flow, with pictures, labs and visualization

Screenshots

Related Topics

1730862

udemy ID

6/4/2018

course created date

11/24/2019

course indexed date

Bot

course submited by