VSD - Pipelining RISC-V with Transaction-Level Verilog

Front end VLSI design can’t get easier than this

4.14 (89 reviews)

744

students

3.5 hours

content

Feb 2018

last update

$34.99

regular price

What you will learn

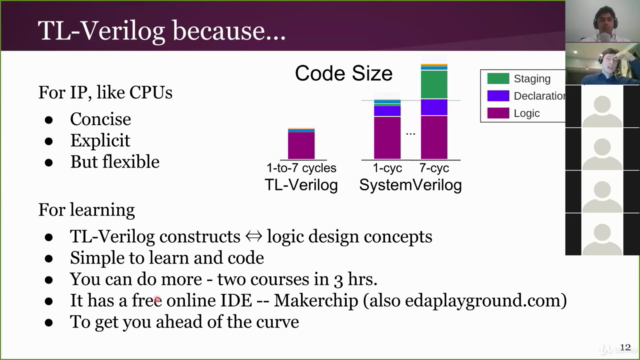

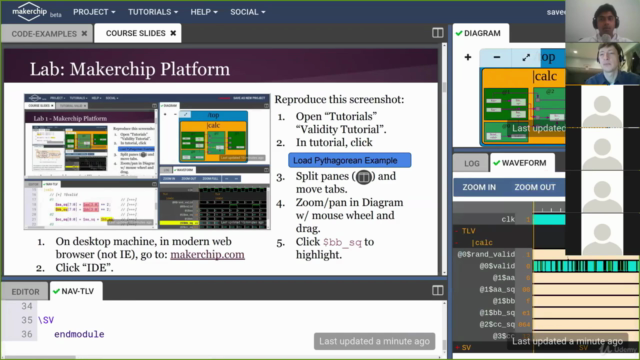

Students will be able to use and implement concepts of pipelining using TL-verilog language and Makerchip platform

Build their own verilog models for IP's using a simpler and powerful Verilog design environment

Screenshots

1549918

udemy ID

2/11/2018

course created date

11/24/2019

course indexed date

Bot

course submited by