VSD - Mixed-signal RISC-V based SoC on FPGA

FPGA flow for Mixed Signal SoC with RISC-V based core and PLL IP

3.88 (8 reviews)

113

students

1.5 hours

content

Jul 2021

last update

$39.99

regular price

What you will learn

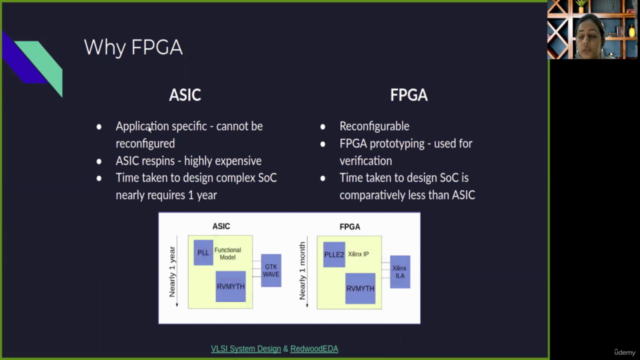

FPGA flow vs ASIC flow

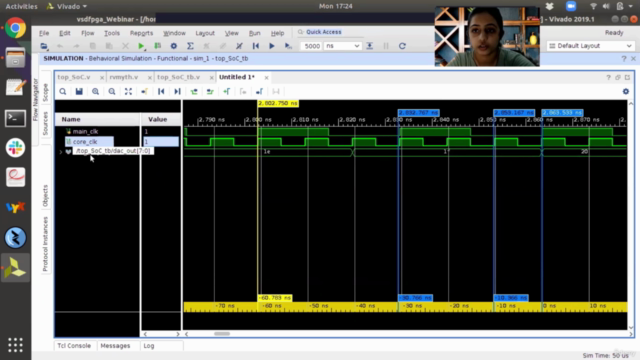

Basic mixed-signal RISC-V based SoC RTL design and simulations

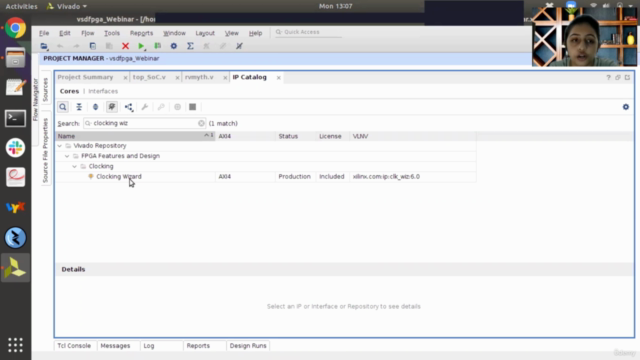

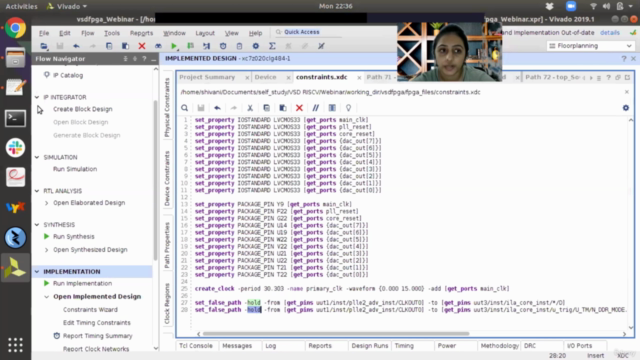

FPGA Synthesis, bit-stream generation and simulation

Screenshots

4185794

udemy ID

7/15/2021

course created date

7/18/2021

course indexed date

Bot

course submited by