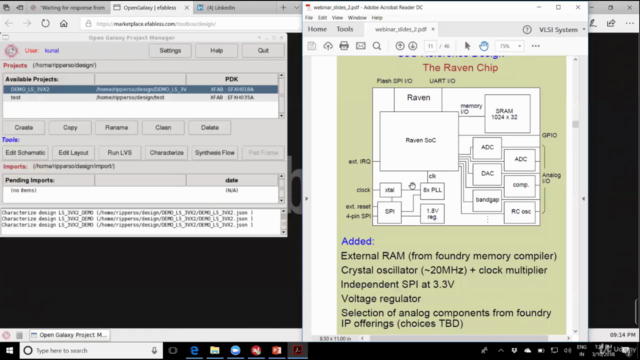

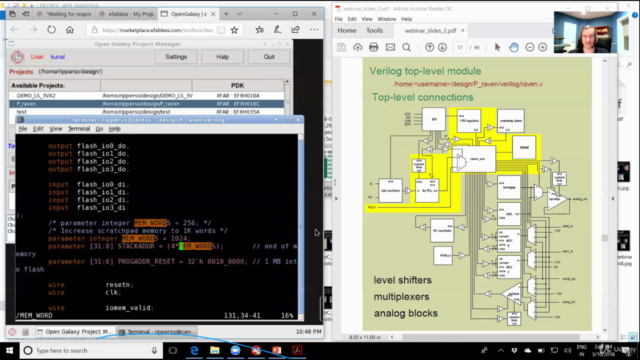

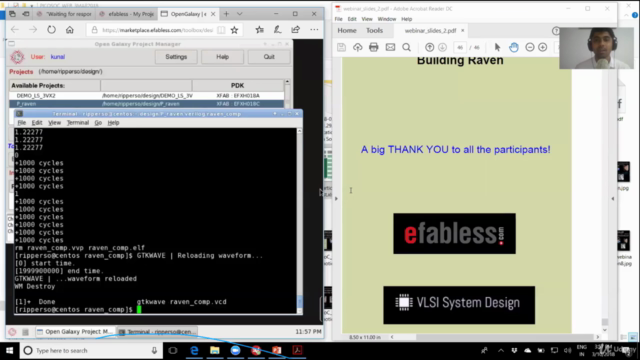

VSD - Making the Raven chip: How to design a RISC-V SoC

Building a chip is like building a city....

4.04 (135 reviews)

1,162

students

4.5 hours

content

Mar 2018

last update

$39.99

regular price

What you will learn

Students will be able to build and configure their own SoC (System-On Chip)

Students will be able to create their own defition of GPIO

Understand decision making process, analog peripheral (ADC, DAC), digital peripheral (UART, flash controller), memory mapping, pad-frame, level-shifters, GPIO

Finally, plan your SoC

Screenshots

1593048

udemy ID

3/12/2018

course created date

11/24/2019

course indexed date

Bot

course submited by