VSD Intern - OpenRAM configuration for 4kB SRAM using Sky130

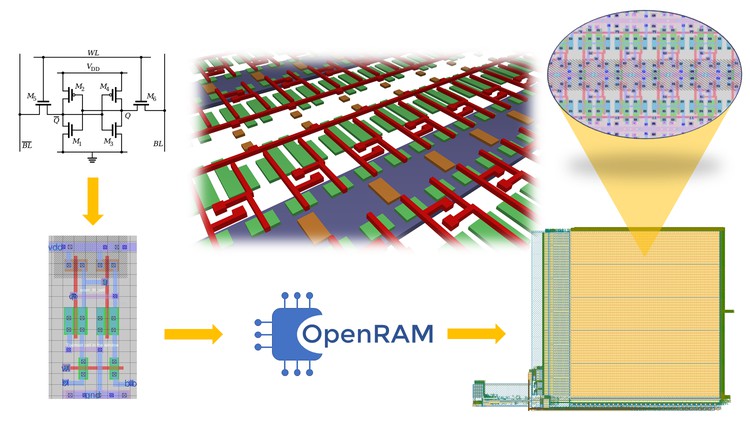

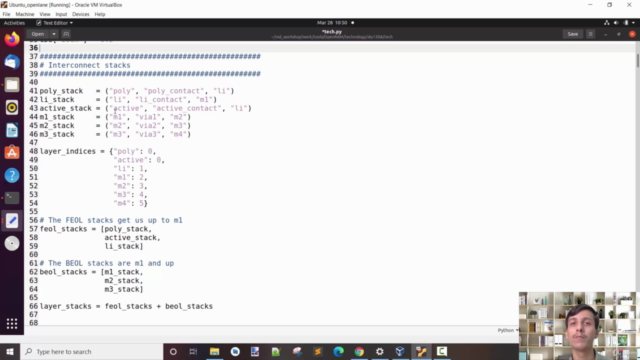

How to configure ope-source compiler OpenRAM for 130nm technology node

3.84 (22 reviews)

220

students

1 hour

content

Apr 2021

last update

$44.99

regular price

What you will learn

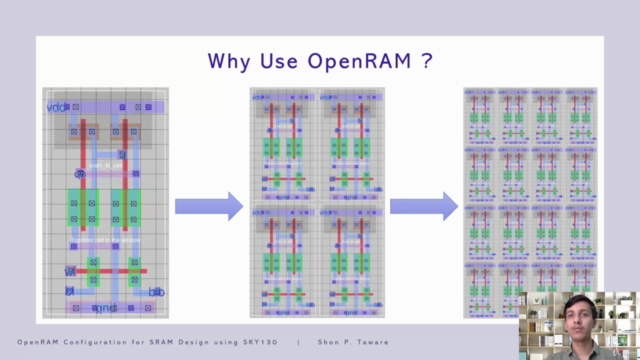

Configure open-source memory compiler OpenRAM for any memory size

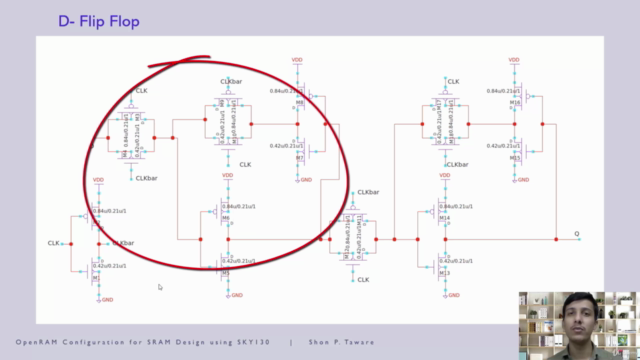

SRAM custom cell design

Memory GDS/Lib/Lef file types

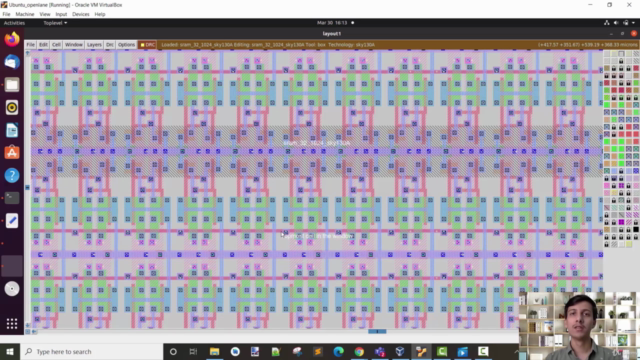

Screenshots

Related Topics

3965020

udemy ID

4/7/2021

course created date

4/13/2021

course indexed date

Bot

course submited by