VSD - Functional Verification Using Embedded-UVM - Part 2

Introduction to object-oriented programming

75

students

1.5 hours

content

Oct 2024

last update

$27.99

regular price

What you will learn

SoC design flow, role of Functional Verification

Logic Modeling, Introduction to Verilog

Concept of Hierarchy, Simulation-Time, and Concurrency in Hardware Modeling

Simulation Technology, Discrete Event Simulation

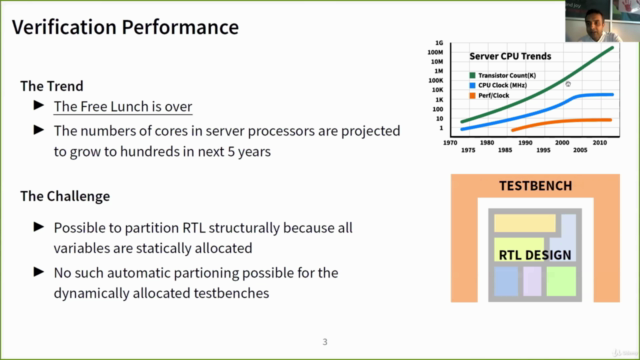

Verification Trends and Challenges

Concepts and Principles of Functional Verification

Testbench Architecture and Components

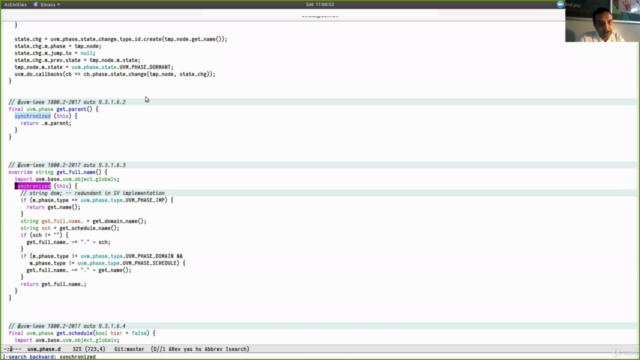

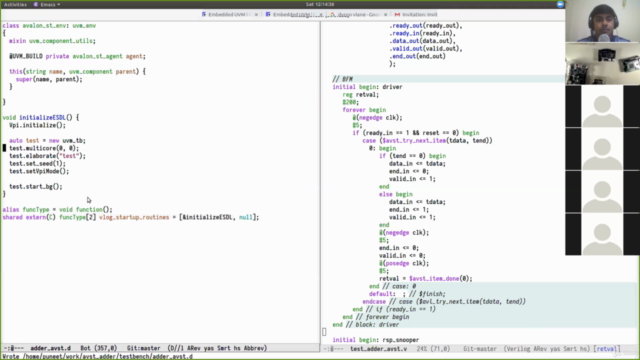

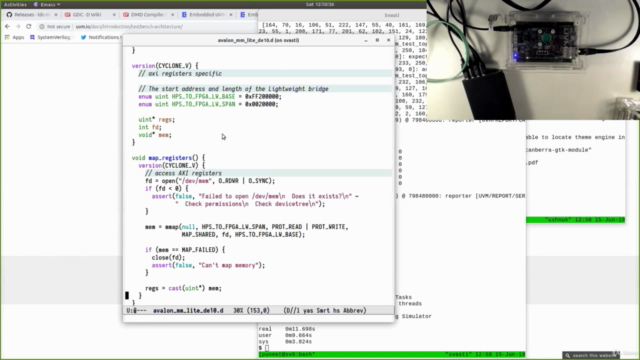

Lab – Tool Setup and Usage -- a simple DUT with traditional Verilog testbench will be provided with a Makefile to compile and simulate – Debug using waveforms

Screenshots

Related Topics

2706780

udemy ID

12/15/2019

course created date

12/17/2019

course indexed date

Bot

course submited by