Verilog ile RTL Tasarımı ve Basys3 FPGA Uygulamaları

#verilog #ASIC #FPGA #sayısaldevretasarımı #Xilinx

What you will learn

Verilog HDL.

RTL Tasarımı.

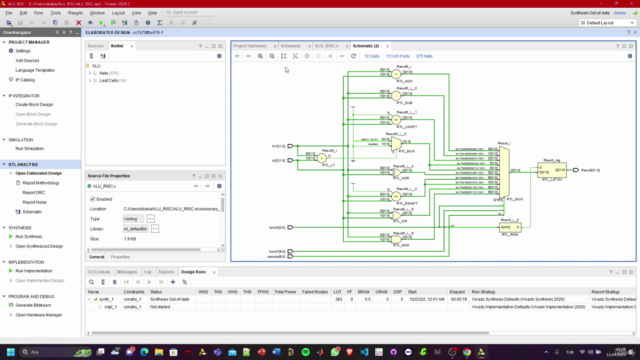

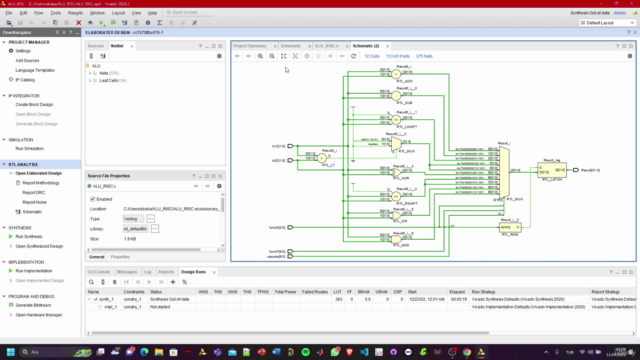

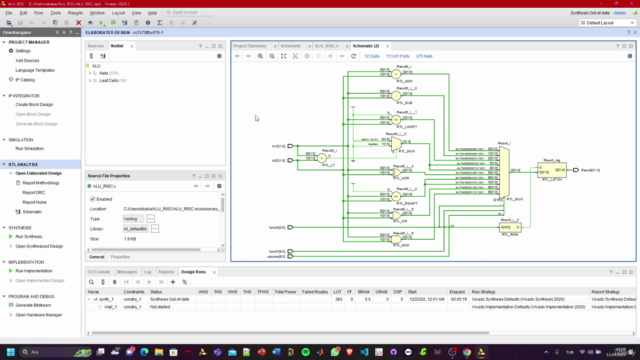

Xilinx Vivado Tasarım Aracı Kullanımı.

Aşama aşama sayısal sistem tasarımı.

C++ dili ile FPGA programlama.

Vitis programı ile IP Modül oluşturma.

Why take this course?

Sayısal devre tasarımı alanı zamanla popülerleşmekte ve popülerleşmeye devam edecektir bu doğrultuda sizler için "Verilog ile RTL Tasarımı" kursu hazırlamaya karar verdim. Kursu belirli süreliğine ücretsiz yayınlamayı istediğim için kurs süresini 2 saat ile sınırladım ancak kurs sürekli güncellenecektir. Türkiyede sayısal devre tasarımı alanının önem kazanmasının en büyük örneği TEKNOFEST yarışması sayısal çip tasarımı yarışma kategorisidir. Kursta tamamen sayısal devre tasarımı üzerinde durulmuştur ayrıca kursa özet bilgisayar mimarisi bölümü eklenecektir bu bölümde sayısal bir çipin alt sistemlerinden bahsedilecektir ve ek olarak bu alt sistemlerin Verilog ile tasarlanması gösterilecektir. Umarım bu kurs sizin için faydalı olur.

Herkese başarılar dilerim, hoşça kalın...

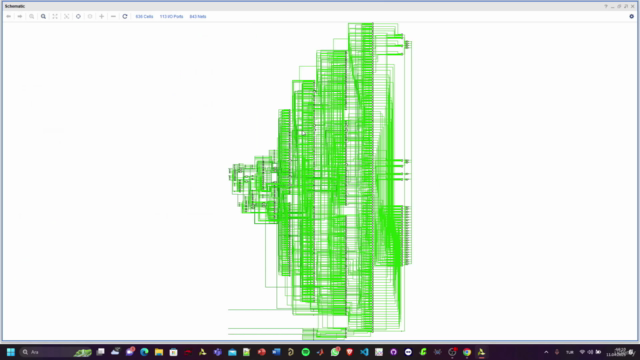

Verilog elektronik sistemleri modellemek için kullanılan bir donanım tanımlama dilidir. Verilog (bazen “Verilog HDL” olarak da adlandırılır) analog, sayısal ve karışık işaretli devrelerin tasarımını, doğrulanmasını ve yürütülmesini değişik düzeylerde desteklemektedir. Verilog dilinin tasarımcıları dilin C programlama diline yakın bir söz dizimine sahip olmasını istemişlerdir. Böylece bu dile yatkın olan mühendislerin dili kolayca kullanmasını amaçlamışlardır. Dil küçük/büyük harf duyarlılığına sahiptir ve temel denetim akışının “if” ve “while” gibi anahtar kelimeleri, C'ye benzemektedir. Verilog birkaç temel yönde C’den farklıdır. Verilog bir blok kodu tanımlamak için kıvrık parantezler yerine Begin/End kullanmaktadır. Verilog 95 ve 2001 işaretçi veya yinelemeli alt yordamlar yapılarına sahip değildir fakat SystemVerilog bu özelliklere sahiptir. Son olarak Donanım Tanımlama Dilleri için çok önemli olan zaman kavramı C dilinde bulunmamaktadır. Verilog geleneksel programlama dilleri gibi basamaklarını tam olarak ardışık bir şekilde yürütmez. Verilog tasarımı modüller arasında bir hiyerarşi bulundurur. Modüller bir takım giriş, çıkış ve çift yönlü portlar şeklinde tanımlanır. Bir modül içinde yazmaç ve kablo listesi bulunur. Eş zamanlı ve ardışık ifadeler modülün davranışını; portların, kabloların ve yazmaçların arasındaki ilişki ile tanımlar. Ardışık ifadeler bir begin/end bloğuna konur ve blokla beraber ardışık olarak yürütülür. Tüm eş zamanlı ifadeler ve begin/end blokları koşut olarak yürütülür. Bir modül aynı zamanda diğer bir modülün bir veya daha çok örneğini içererek bir alt-davranışı belirtebilir. Eğer tasarımdaki modüller sadece sentezlenebilir ifadeler içeriyorsa bu tasarımın donanımda gerçekleştirilecek temel bileşenlerini ve bağlantılarını içeren netlist, yazılım sayesinde sentezlenebilir. Elde edilen bu netlist bir tümleşik devreyi (örn. ASIC veya FPGA) tanımlamak amacıyla kullanılabilir.

Screenshots

Charts

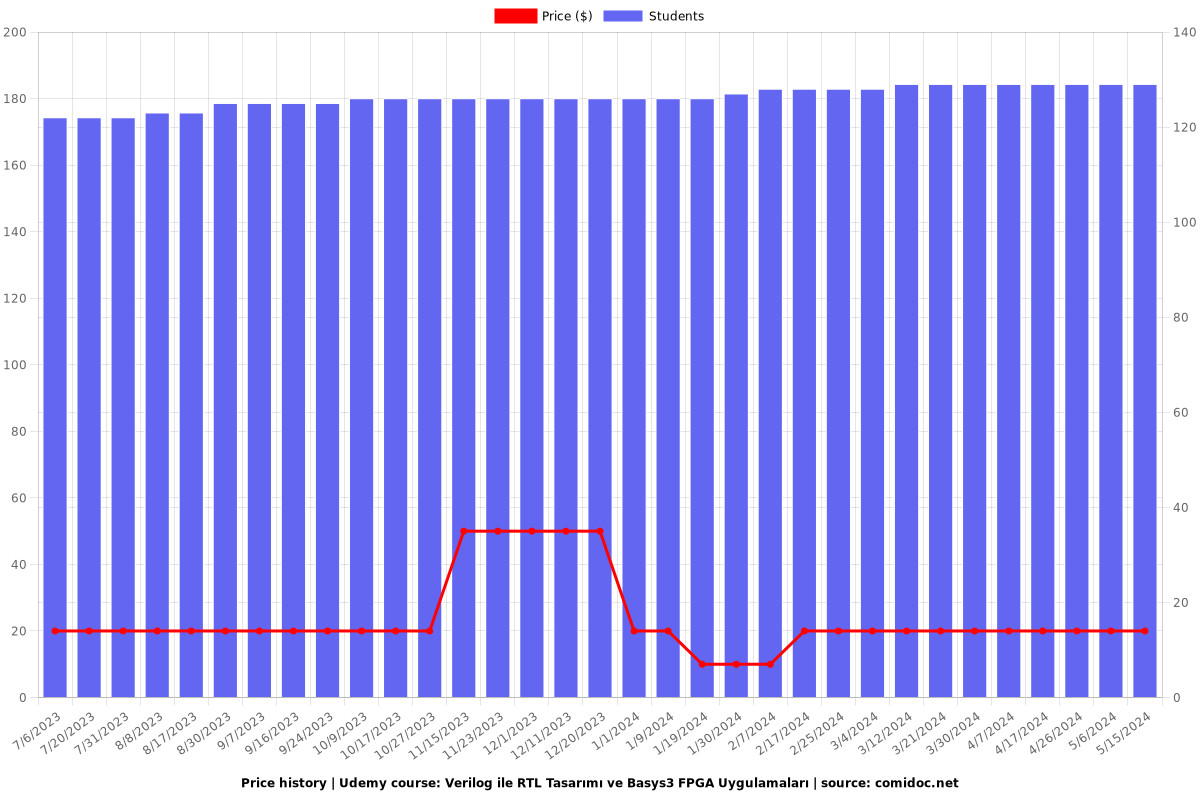

Price

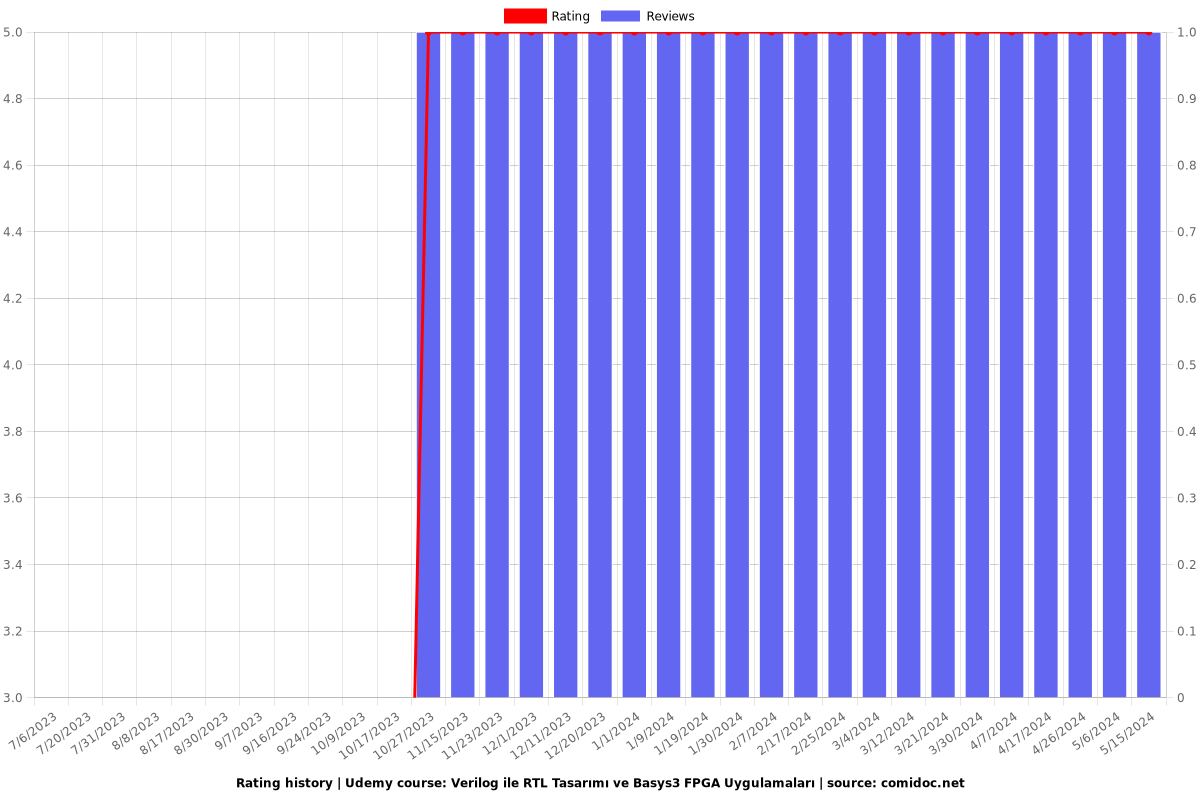

Rating

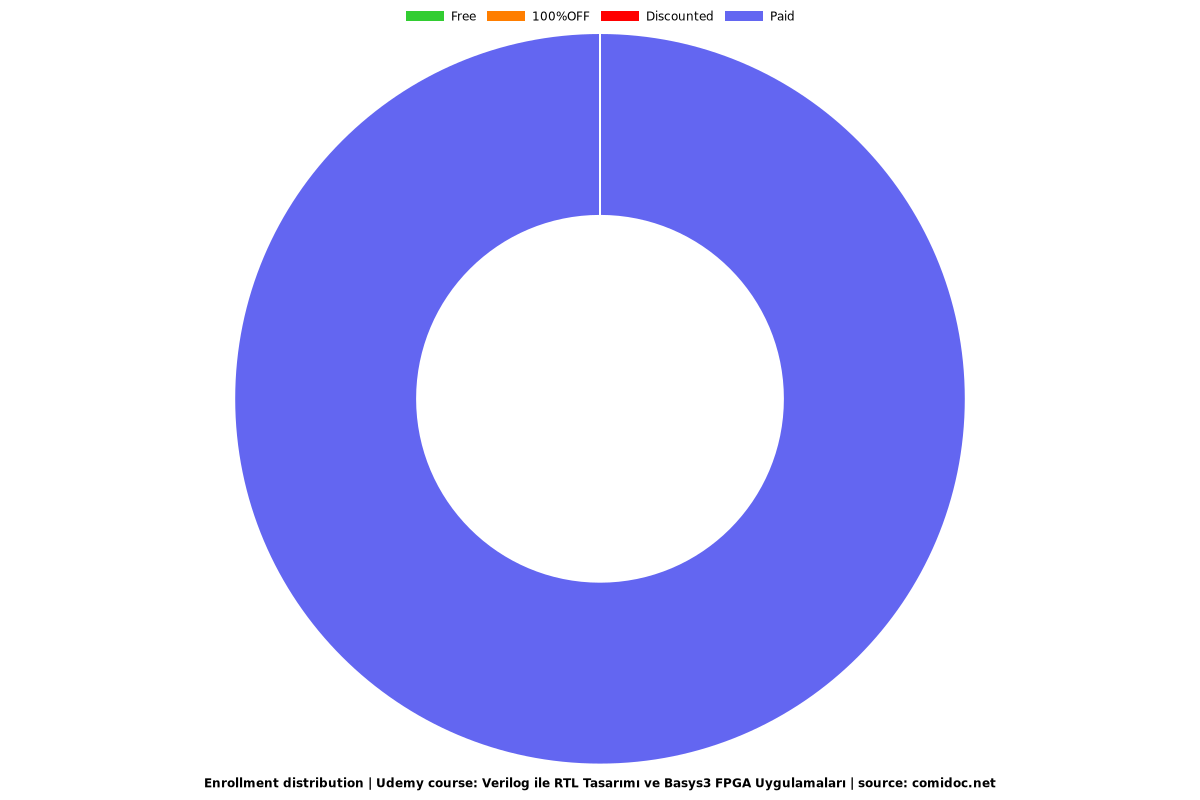

Enrollment distribution