Verilog for an FPGA Engineer with Xilinx Vivado Design Suite

Using Xilinx FPGA's

4.48 (1598 reviews)

10,414

students

16.5 hours

content

Jan 2025

last update

$84.99

regular price

What you will learn

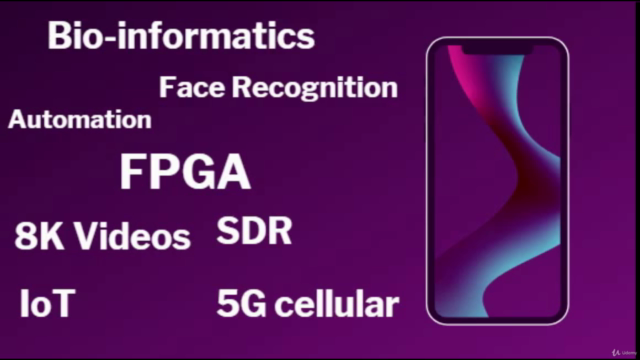

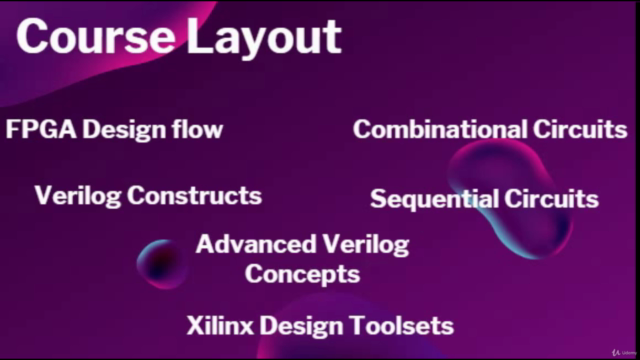

Fundamentals of Verilog Programming that will help to ace RTL Engineer Job Interviews.

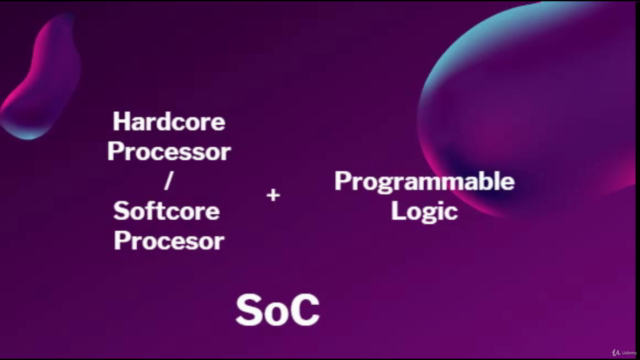

Understand Vivado Design Suite flow for Digital System Design.

Hardware Debugging in Vivado viz. Integrated Logic Analyzer, Virtual I/O.

Different Modelling Styles in Hardware Description Language.

How to use Xilinx IP's and create Custom IP's.

IP integrator Design flow of the Vivado.

Writing Verilog Test benches.

Design of some real world projects such as : PMOD DA4 DAC interface, Function Generator, Small Processor Architecture, UART Interface, PWM, BIST for Development boards and many more.

Common Interview Questions

Screenshots

Related Topics

2940044

udemy ID

3/31/2020

course created date

9/10/2020

course indexed date

Bot

course submited by