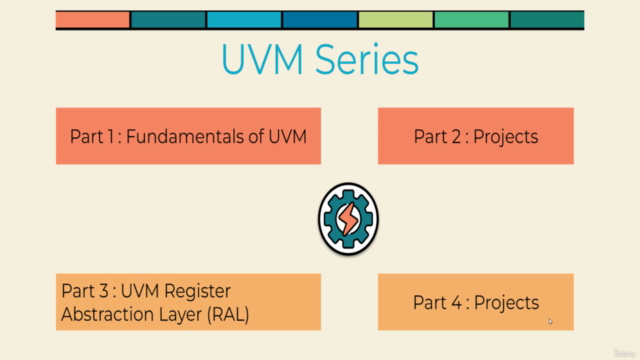

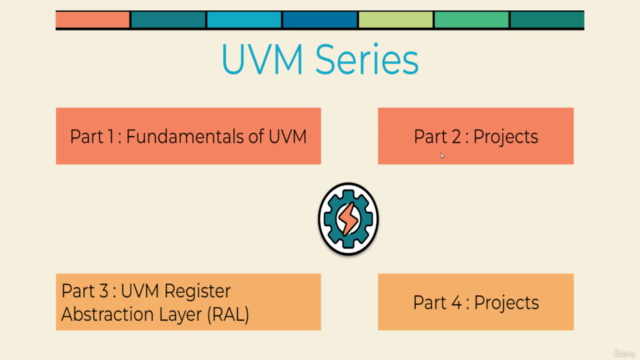

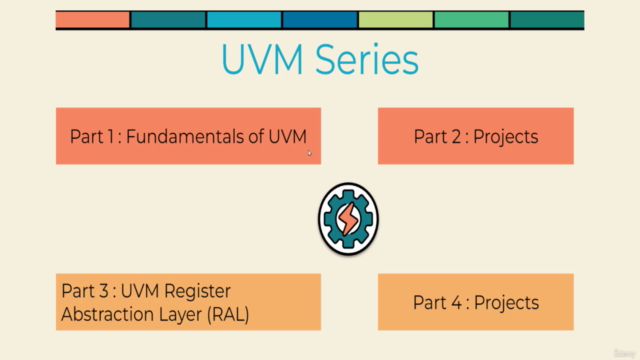

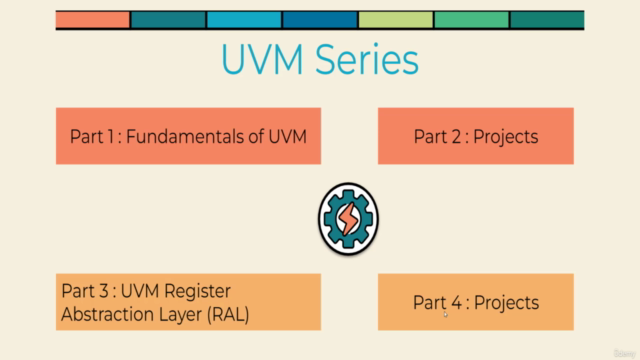

Verification Series Part 3: UVM Essentials

Step by Step Guide from Scratch

4.70 (1317 reviews)

7,730

students

11 hours

content

Jan 2025

last update

$79.99

regular price

What you will learn

Fundamentals of Universal Verification Methodology

Reporting Macros and associated actions

UVM Object and UVM Component

UVM Phases

TLM Communication

Sequences

UVM Debugging features

Building UVM Verification Environment from Scratch

Screenshots

Related Topics

4744280

udemy ID

6/21/2022

course created date

10/26/2022

course indexed date

Bot

course submited by