SystemVerilog using Object Oriented Programming

Simple course for students and engineers who wants to learn Object Oriented Programming concepts in SystemVerilog.

3.88 (4 reviews)

59

students

8.5 hours

content

Apr 2021

last update

$24.99

regular price

What you will learn

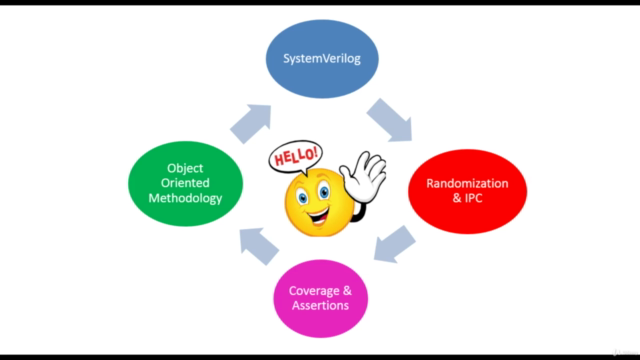

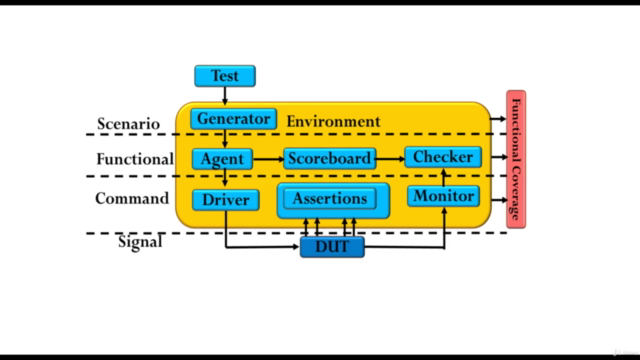

Concept of Layered Testbench

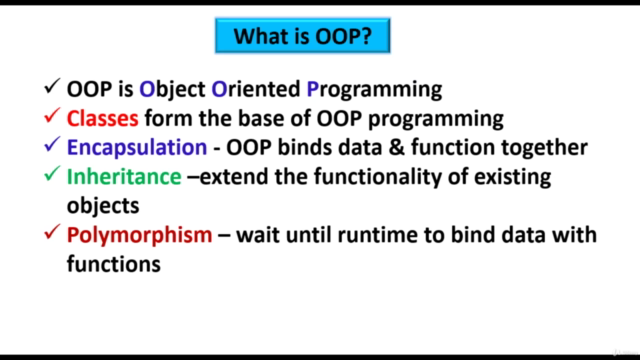

Introduced to Basic Terminologies of Object Oriented Programming

Write your own Class and use it in Testbench

Concepts of Static Variables, Methods and various Scoping Rules

Learn how to implements concepts like inheritance in SystemVerilog

Concepts of Direct Programming Interface (DPI)

Interfacing between C and SystemVerilog

Interfacing between C++ and SystemVerilog

Screenshots

Related Topics

3032828

udemy ID

4/21/2020

course created date

5/6/2021

course indexed date

Bot

course submited by