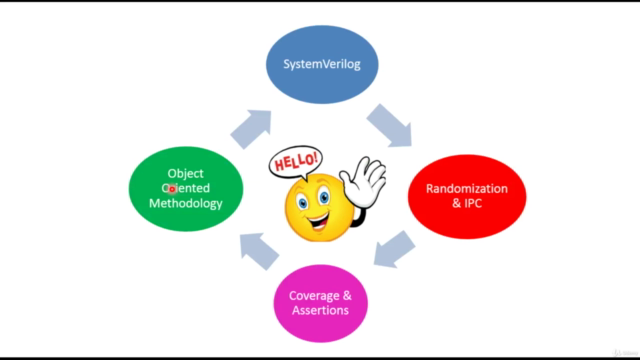

Randomization and IPC in SystemVerilog

Simple course to learn advanced verification technique of Randomization and IPC in SystemVerilog.

4.36 (7 reviews)

67

students

12.5 hours

content

Apr 2021

last update

$24.99

regular price

What you will learn

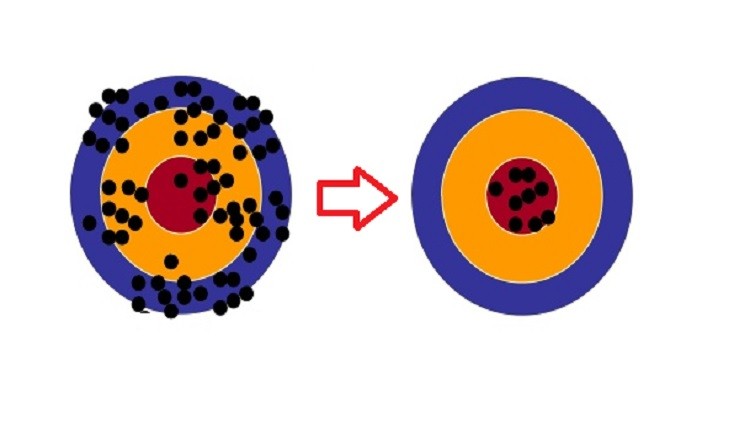

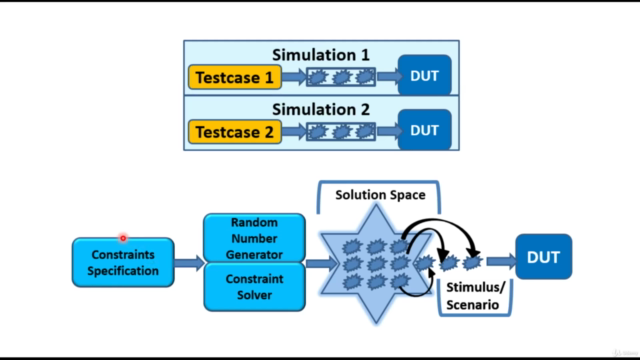

Difference between directed and random testing

What is randomization and why verifiation engineer should know it

How to do ramdomization in SystemVerilog

How to do constrained randomization

Various options available during randomization

How control thread execution happens in Verilog

Event communication in SystemVerilog

Semaphore in SystemVerilog

Mailboxes in SystemVerilog

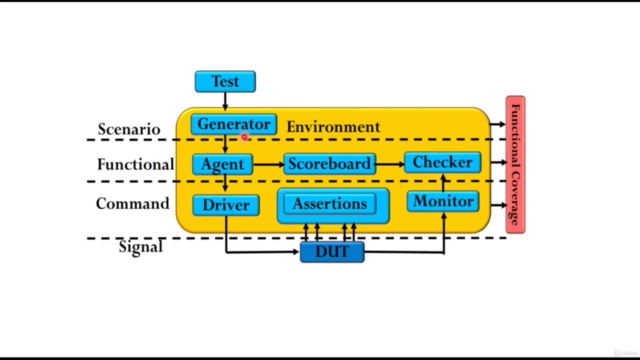

How to write Testbench using IPC

Screenshots

Related Topics

3028548

udemy ID

4/20/2020

course created date

5/6/2021

course indexed date

Bot

course submited by