Fundamentals of Verification and System Verilog

Simple course for students and engineers who wants to learn concepts of verification and basic SystemVerilog Constructs

4.20 (91 reviews)

800

students

21.5 hours

content

Jul 2020

last update

$24.99

regular price

What you will learn

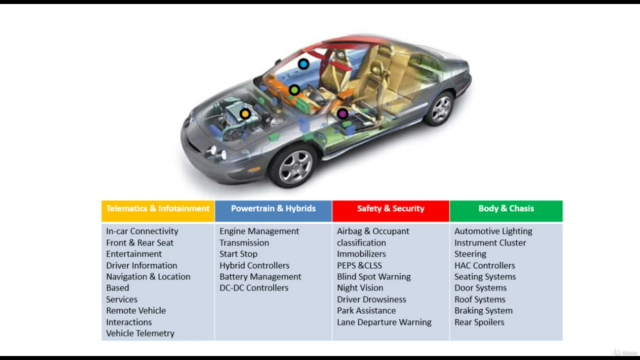

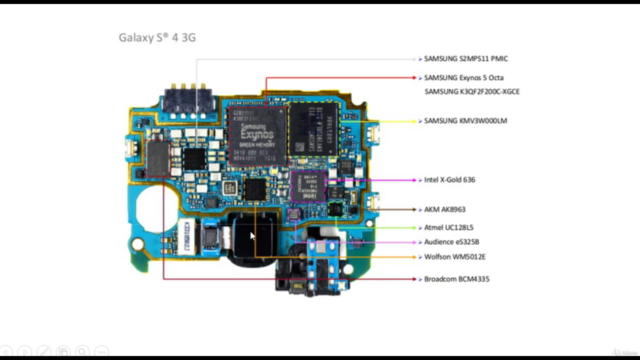

Significance of verification

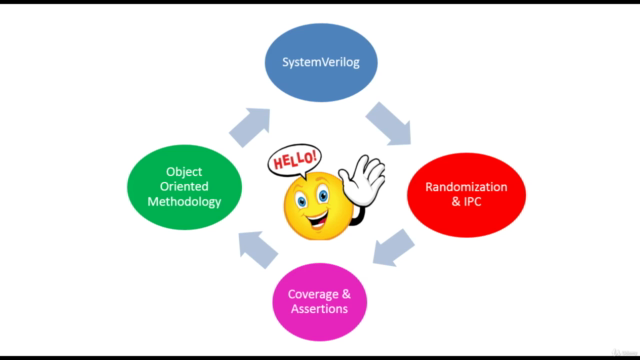

Verification options, methodologies, approaches and plan

Examples to practice on verification tool EDA Playground

Testbench Fundamentals

Writing your SystemVerilog code

Various SystemVerilog Data Types including User Defined Data Types

Procedural Statements

Interface Concepts

Screenshots

Related Topics

3032780

udemy ID

4/21/2020

course created date

8/14/2020

course indexed date

Bot

course submited by