Functional Coverage and Assertions in SystemVerilog

Simple and useful course for students and verification engineers to learn functional coverage and assertions.

3.75 (4 reviews)

49

students

8.5 hours

content

Apr 2021

last update

$24.99

regular price

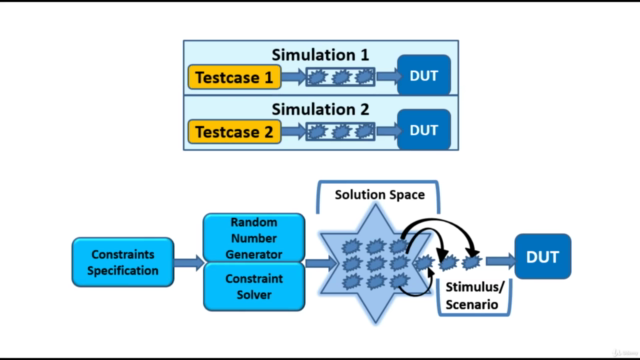

What you will learn

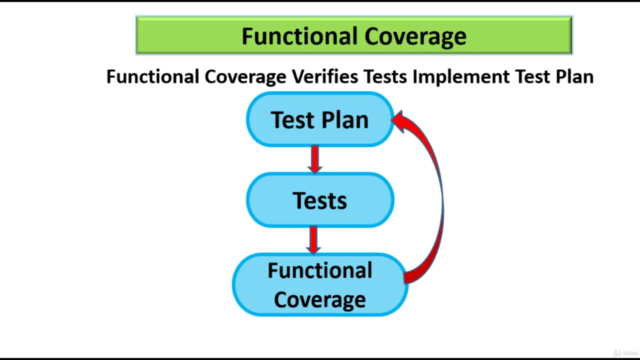

Significance of Coverage

Various Types of Coverage

How to do Functional Coverage

Cross Coverage and other importance concepts related to Functional Coverage

How Learning Assertions to Verification Engineer

Types of assertions

How to write assertions

How to do Assertion Based Verfication (ABV) using SystemsVerilog Assertions (SVA)

Screenshots

Related Topics

3032834

udemy ID

4/21/2020

course created date

5/6/2021

course indexed date

Bot

course submited by