Xilinx VIVADO Beginner Course for FPGA Development in VHDL

Learn how to Create VHDL Design,Simulation Testbench & Implementation with Xilinx VIVADO & FPGA: from Basic to Advanced.

3.67 (55 reviews)

460

students

5 hours

content

May 2019

last update

$49.99

regular price

What you will learn

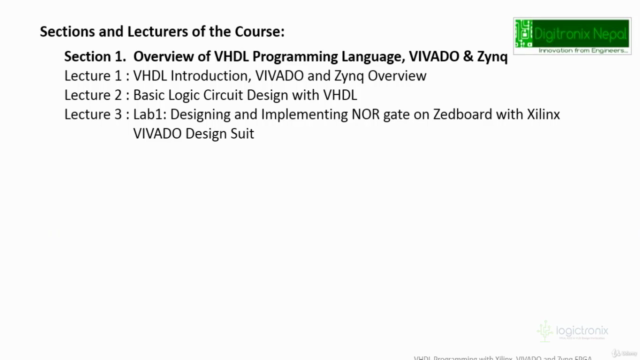

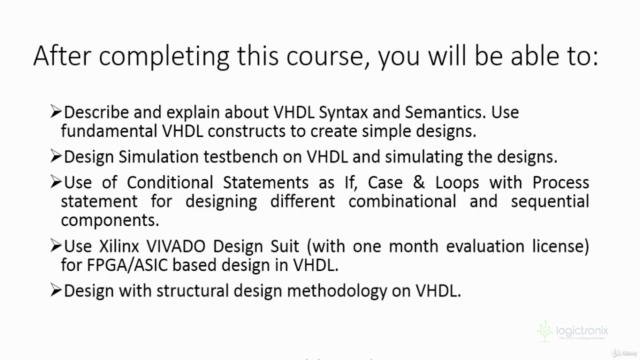

Idea of VHDL Programming , VIVADO Design Methodology and Designing/Implementing Design in Zynq FPGA-ZedBoard

Use fundamental VHDL constructs to create simple designs. Understanding the Conditional Statements in VHDL.

Design Simulation testbench on VHDL and simulating the designs.

Design with structural design methodology on VHDL.

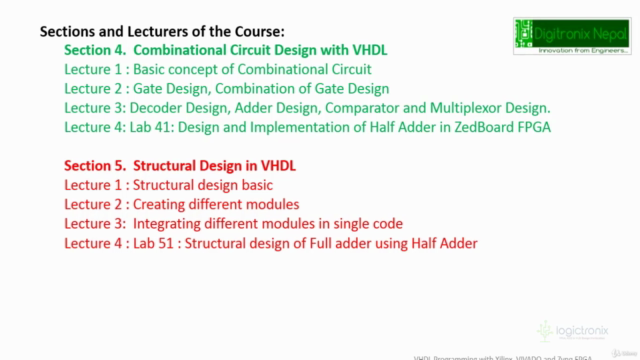

Designing Decoder, Adder, Register and Counter in VHDL and Implementing in ZedBoard

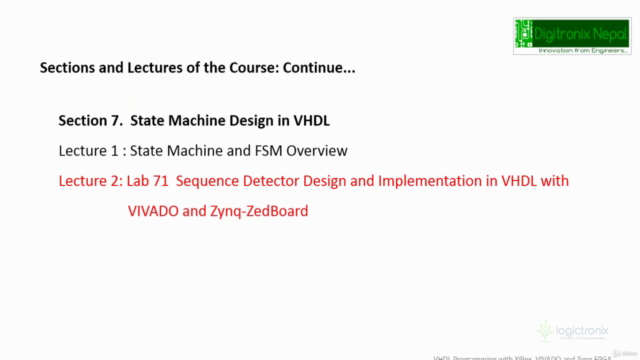

Implementing State Machine in VHDL; Designing/Implementing Sequence Detector

Screenshots

1138728

udemy ID

3/8/2017

course created date

11/22/2019

course indexed date

Bot

course submited by