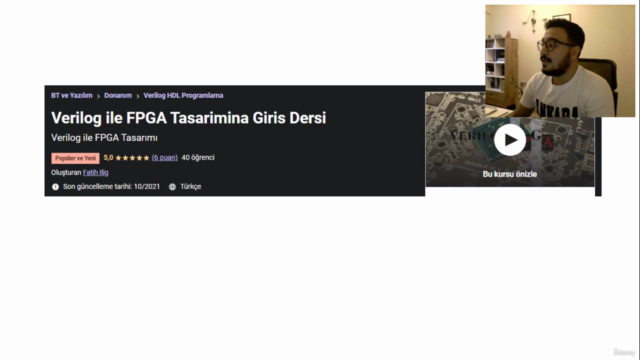

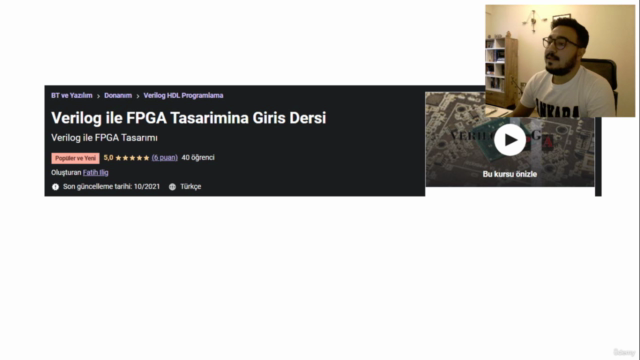

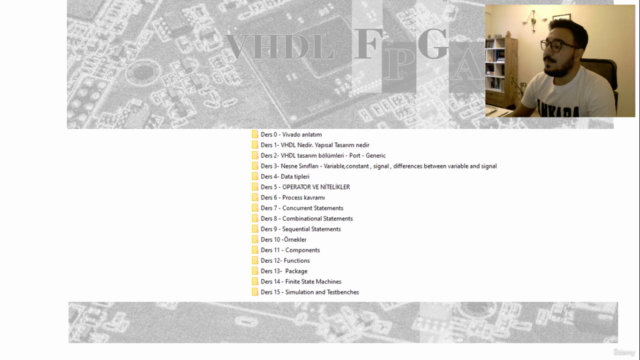

VHDL ile FPGA Tasarimina Giris Dersi - Bolum 1

7 Bolumden olusan VHDL dili kursuna basliyoruz.

4.60 (109 reviews)

1,505

students

1 hour

content

Oct 2024

last update

FREE

regular price

What you will learn

VHDL Dili ile Donanım Tasarımı yapmak

VHDL ile Combinational, Sequential devreler yaratarak RTL model tasarlamak, Finite State machine yapılarını öğrenmek

Xilinx Vivado kullanarak Simülasyonlar yapmak

Test bench ve Verification Methodology kavramlarını anlamak

FPGA yapılarını (Register, Flip Flop, gates) verilog dili ile yaratmak ve kullanımını öğrenmek

Örneklerle VHDL dilini pekiştirmek ve ilerletmek

Screenshots

4403495

udemy ID

11/18/2021

course created date

12/3/2021

course indexed date

Bot

course submited by