Learn Verilog with Xilinx VIVADO Tool

Learn Verilog Programming from top to bottom with Xilinx VIVADO Design Suite for FPGA Development

3.74 (110 reviews)

699

students

4.5 hours

content

Mar 2021

last update

$49.99

regular price

What you will learn

Learn and understand about Verilog Programming Language

Verilog Design Flow and its Syntax/Semantics

Creating Basic Logic Gates in Verilog

VIVADO Design Flow for FPGA Design with Verilog

Understand Conditional Statement in Verilog

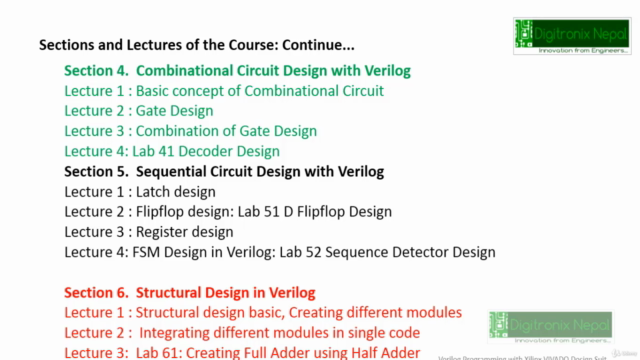

Combinational and Sequential Circuit Design with Verilog

Finite State Machine Design with Verilog

Structural Modeling/Design with Verilog

Screenshots

Related Topics

1380770

udemy ID

10/5/2017

course created date

11/22/2019

course indexed date

Bot

course submited by