High-Level Synthesis for FPGA, Part 3 - Advanced

Logic Design with Vitis-HLS

4.51 (73 reviews)

1,087

students

7.5 hours

content

Jan 2023

last update

$79.99

regular price

What you will learn

Using Multi-Cycle design flow to develop sequential circuits in HLS.

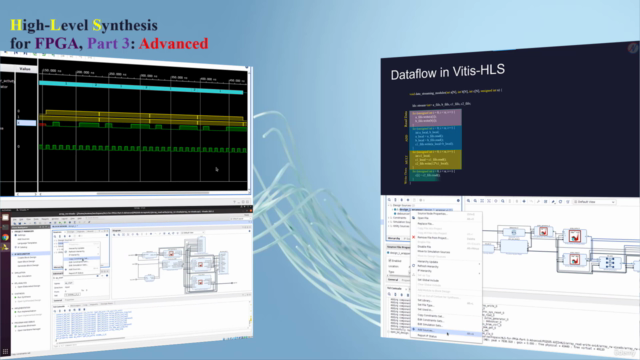

Implementing stream communication and computation in HLS

Using FIFO as the synchronisation mechanism between to connected module

Learning how to use an array variable inside an HLS code

Connecting and AND HLS IP to BRAMs in a Vivado project

Working with pointers in HLS

Working with AXI protocol in HLS

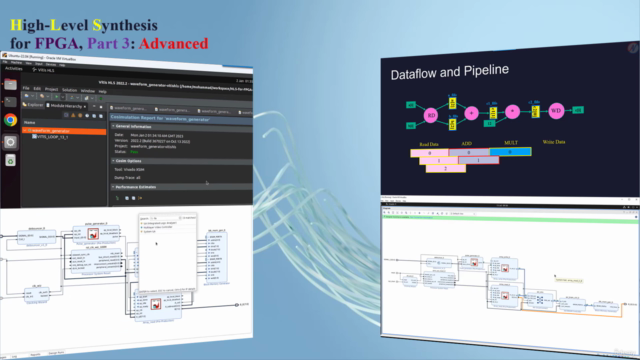

Loop pipelining optimisation in HLS

Loop unrolling optimisation in HLS

Loop flattening optimisation in HLS

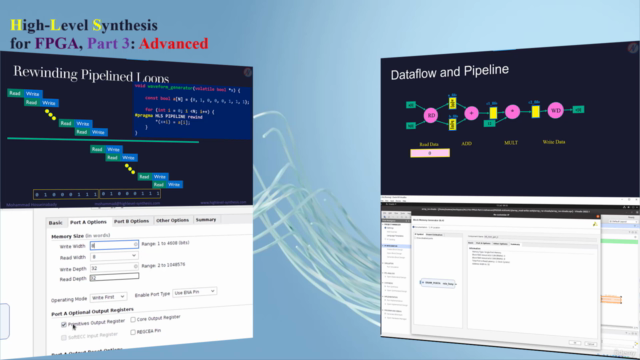

Loop rewinding optimisation in HLS

Working with the HLS-Stream library in HLS

Handshaking protocol and interfaces in HLS

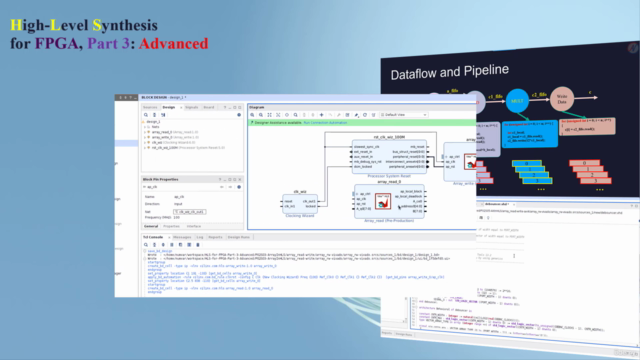

Screenshots

5061926

udemy ID

1/5/2023

course created date

1/29/2023

course indexed date

Bot

course submited by