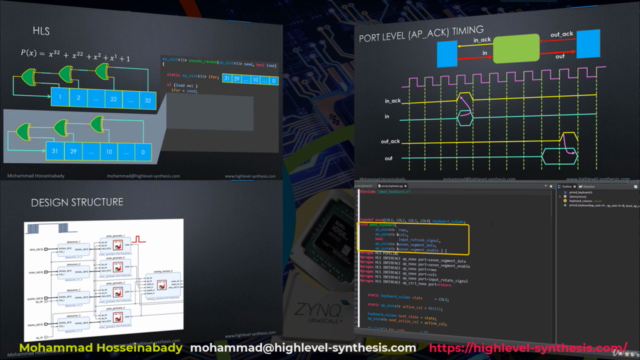

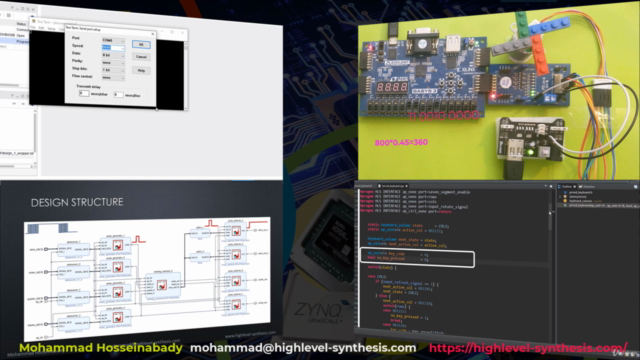

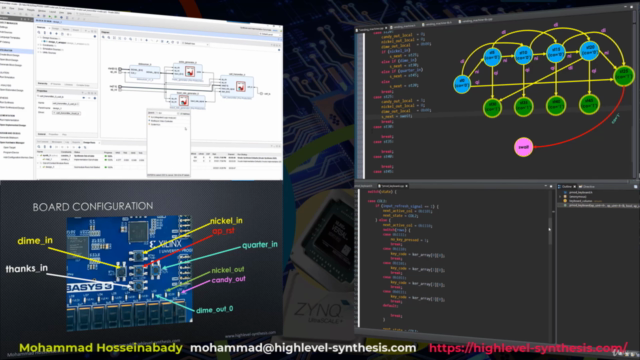

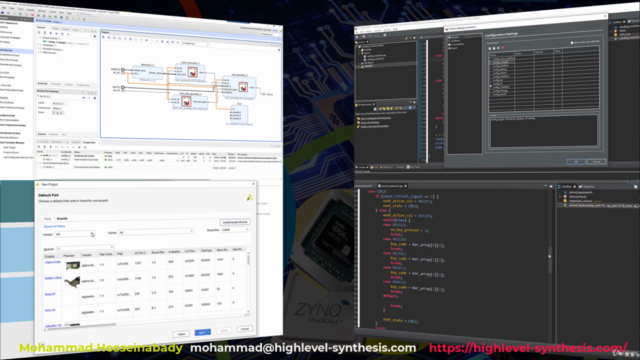

High-Level Synthesis for FPGA, Part 2 - Sequential Circuits

Logic Design with Vitis-HLS

4.65 (161 reviews)

2,165

students

9.5 hours

content

Mar 2023

last update

$74.99

regular price

What you will learn

Designing sequential logic circuits with C/C++ language using the HLS approach

Understanding the basic concepts of High-Level Synthesis (HLS)

Using HLS concepts for designing sequential logic circuits

HLS design flow for FPGAs

Working with Xilinx Vitis-HLS and Vivado design suite Toolsets

How to generate RTL hardware IPs using Vitis-HLS

Writing C-testbench in HLS

Implementing three exciting projects with HLS

Screenshots

Related Topics

3639976

udemy ID

11/17/2020

course created date

3/30/2021

course indexed date

Bot

course submited by