FPGA Design with VIVADO HLS -High Level Synthesis

Design, Simulate, Synthesize & Export IP with VIVADO HLS : An FPGA Design Approach with C/C++

3.25 (94 reviews)

622

students

4 hours

content

Mar 2023

last update

$49.99

regular price

What you will learn

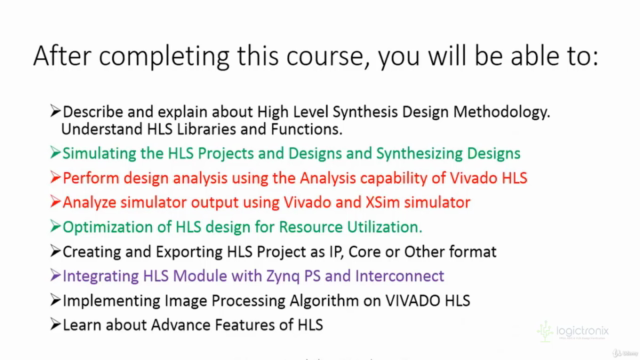

Vitis HLS Installation, OpenCV Setup and LAB session

Image Processing with VIVADO HLS & FPGA: Utilizing Computer Vision & Image/Video Processing Libraries on HLS

Sobel Edge Detection IP design in HLS, integrate IP in VIVADO tool and implement it on Zynq FPGA

Designing complete image processing pipeline on VIVADO tool with HLS IP and testing design on Zynq FPGA

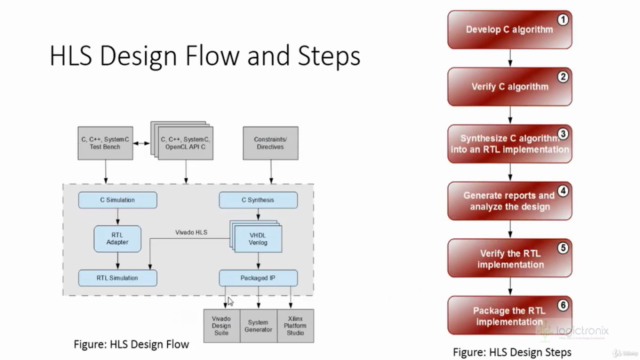

Creating C/C++ Project, Simulating, Synthesizing and Exporting it with High Level Synthesis (VIVADO HLS)

Design, Synthesize, Simulate: Counter, Matrix Multiplier, Frequency Modulator ,Numerically Controlled Oscillator and Exporting Design to VIVADO tool

Debugging and Optimizing HLS Project for Resource Utilization on Targeted ZedBoard FPGA

Screenshots

1248160

udemy ID

6/10/2017

course created date

11/22/2019

course indexed date

Bot

course submited by