Develop and analyze a SIMULINK model from scratch

Live model development and analysis from hand-written requirements made for beginners

4.17 (3 reviews)

168

students

6 hours

content

Nov 2020

last update

$34.99

regular price

What you will learn

Capture a set of raw requirements and make a design flow diagram for a timer.

Select the SIMULINK blocks required for the design and start developing the model from scratch.

Identify and analyze potential pitfalls in the model and fix bugs.

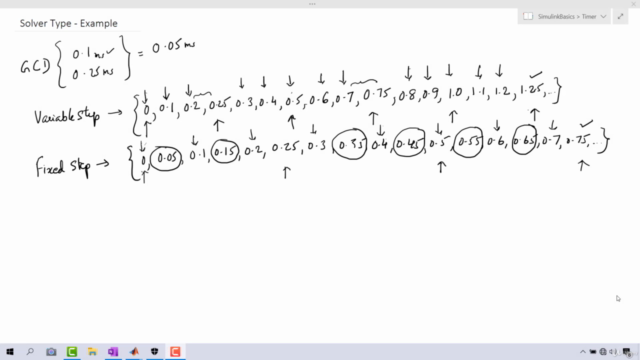

Learn some of useful concepts and features of SIMULINK as we go.

Screenshots

3466206

udemy ID

9/1/2020

course created date

10/28/2022

course indexed date

Bot

course submited by