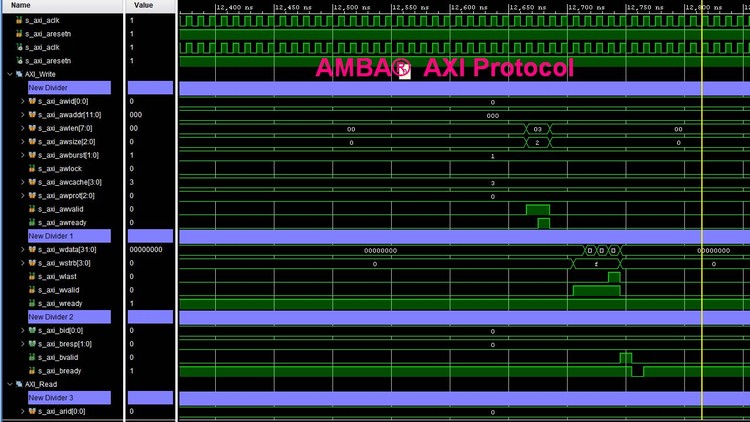

AMBA AXI Infrastructure Based on Xilinx FPGA IPs and Verilog

Explanation of AMBA AXI protocol based on Xilinx Infrastructure, verilog and System verilog

4.26 (182 reviews)

1,244

students

4 hours

content

Jul 2020

last update

$34.99

regular price

What you will learn

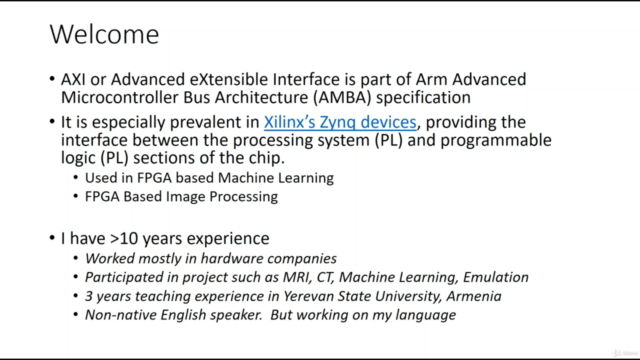

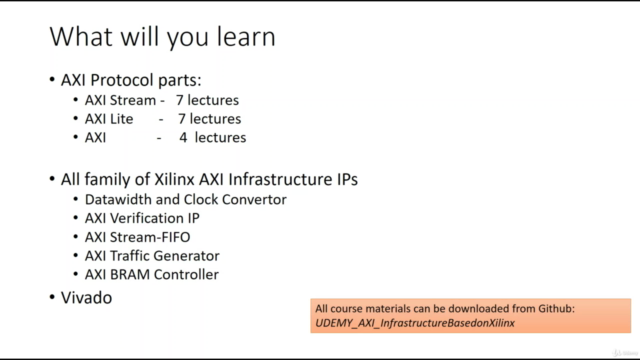

ARM AXI Protocol

Xilinx AXI Infrastructure

Xilinx Vivado Tool

FPGA and Verilog

Zynq

System Verilog

Screenshots

2145944

udemy ID

1/12/2019

course created date

4/11/2021

course indexed date

Bot

course submited by